Віртуальний осцилограф

Дана розробка замислювалася як доповнення до вже існуючого аналогового осцилографа для дослідження рідкісних і неперіодичних ВЧ сигналів. Вона виконана у вигляді приставки до ПК. При проектуванні особлива увага приділялася доступності та низької вартості компонентів.

Залізо:

Принцип роботи цифрового осцилографа досить простий. Необхідно швидко забити мікросхему пам'яті даними, а потім досить повільно передавати їх по послідовному каналу в комп'ютер для відображення і вимірювань.

Схема генератора і дільника тактової частоти

U1-генератор тактової частоти 20МГц, його вихід підключається до лічильника U2, U3. Коефіцієнт розподілу частоти 1 ... 128 вибирається мультиплексором U4.

Схема запуску і формування адреси

Мультиплексор U1 вибирає джерело синхронізації: мікропроцесор, компаратор рівня або зовнішній імпульс. На U2 реалізована схема запуску і зупинки перетворення. Коли система буде готова до нового пріобразованію, то мікроконтролер подає дозволяє імпульс на тригер U2A. При надходженні переднього фронту імпульсу синхронізації на тактуючий вхід U2B комутатор U3 переключається на тактовий сигнал і лічильник U4-U7 починає перебирати адреси. Коли лічильник послідовно перебере весь діапазон адрес, то інвертором U8 буде сформований сигнал скидання і відключення тактирования. У цей момент лічильник перемикається комутатором U3 на тактирование від контролера для читання і передачі даних в ПК.

схема контролера

Дані записуються в мікросхему пам'яті типу SRAM U1 UM61256K-15, яка була висмикнута з материнки від 486-го комп'ютера. При читанні мікросхема пам'яті працює в режимі, керованим адресою. В цьому режимі шинний формувач U5 переходить в третій стан і забороняє проходження цифрових сигналів від АЦП або від досліджуваної схеми в режимі логічного аналізатора. МК U4 формує сигнал тактирования лічильника, зчитує вміст мікросхеми пам'яті і послідовно передає його в ПК через UART. При записи вихід пам'яті переходить в третій стан (/ OE = 1), U5 дозволяє проходження сигналів, а вхід записи U1 (/ WE) тактується основним тактовим сигналом.

Дані в ПК передаються зі швидкістю 115200 бод. Оскільки для передачі всього вмісту чіпа пам'яті буде потрібно близько трьох секунд (32 кілобайт), то передбачено 2 режими передачі: часткова передача (передається 1 кілобайт, перемичка на вив. 1 U4 розімкнути) і повна передача (перемичка замкнута). Спочатку замислювалося 2 каналу (PORTC для другого чипа пам'яті), але поки я зупинився на одному.

Схема аналогової частини

На U1 реалізований підсилювач вертикального відхилення. R5 і C2 підбираються по мінімуму ВЧ дзвону. Треба сказати, що в рекомендованою схемою включення C2 відсутня. Однак в ході експериментів виявилося що його додавання покращує перехідні процеси. C4 підбирається для зменшення посилення і підвищення стабільності на високих частотах. Смуга пропускання по рівню 0дб вийшла 4МГц. Радянські мікросхеми йдуть з дуже великим розкидом параметрів, тому потрібно підбір примірника U1 за мінімальним часом встановлення і хорошій швидкості наростання. Я пробував в схемі швидкі ОУ LM318, які за характеристиками на кшталт краще. Але виявилося, що відібраний ОУ 574УД1 працює набагато краще, хоча у різних мікросхем LM318 частотні параметри досить стабільні. Змінним резистором RV3 регулюється зміщення спостережуваного сигналу вгору-вниз. На U2 зібраний компаратор системи синхронізації. LM311 має час встановлення 200нс, якого цілком достатньо для роботи на частотах до 5-10 мегагерц. При бажанні можна використовувати і більш швидкодіючі компаратори. Резистором RV1 встановлюється необхідний рівень синхронізації. У схемі застосований швидкий (на ті часи) радянський паралельний АЦП К1107ПВ2 (на схемі не показаний). Схема включення АЦП - стандартна з ДШ. Його можна замінити на 1107ПВ1А зі зменшенням розрядності до 6 біт (у випадку з К1107ПВ1Б максимальна швидкість буде в 2 рази нижче - 10 мегавиборок / сек). Резистором RV2 налаштовується опорна напруга --2 вольта для АЦП. Аналогова частина має незакінчений вигляд, тут відсутній захист від перенапруги по входу, захист АЦП, немає вхідного дільника і вхідний опір не набагато більше кілоомах. Втім це не заважає вимірювати низьковольтні сигнали від джерел з малим вихідним опором в десятки-сотні ом.

Схема блоку живлення

Біполярний БП без особливостей. Тільки трансформатор слід вибирати досить потужний тому одна мікросхема АЦП споживає струм 0,5 А.

Исходник для Atmega8515

Конструкція була зібрана на трьох макетних платах, ніякі печатки не розроблялись.

Софт:

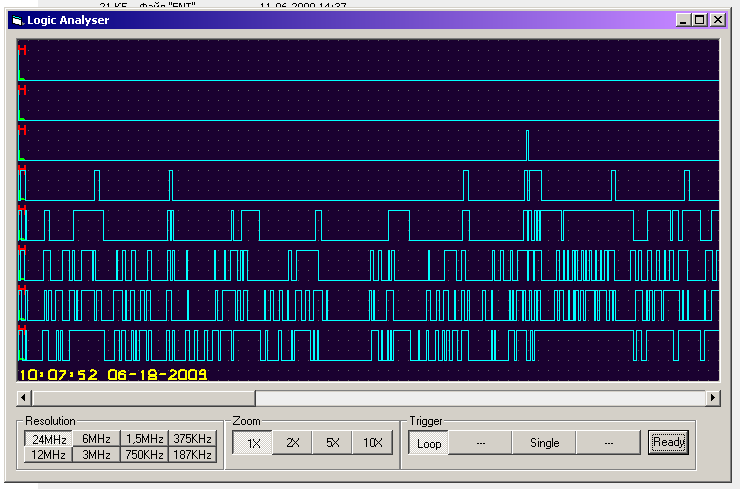

Для перевірки працездатності цифрової частини була написана програма логічного аналізатора.

Досліджувані цифрові дані подаються на вхід шинного формувача замість АЦП.

исходник аналізатора

Спочатку я використовував готовий кварцовий генератор на 48 МГц. Ця частота ділилася до 24МГц. Але після підключення АЦП я побачив що це для нього забагато (крім того схема не забезпечує необхідну шпаруватість тактового сигналу). В результаті частота була знижена до паспортних 20МГц.

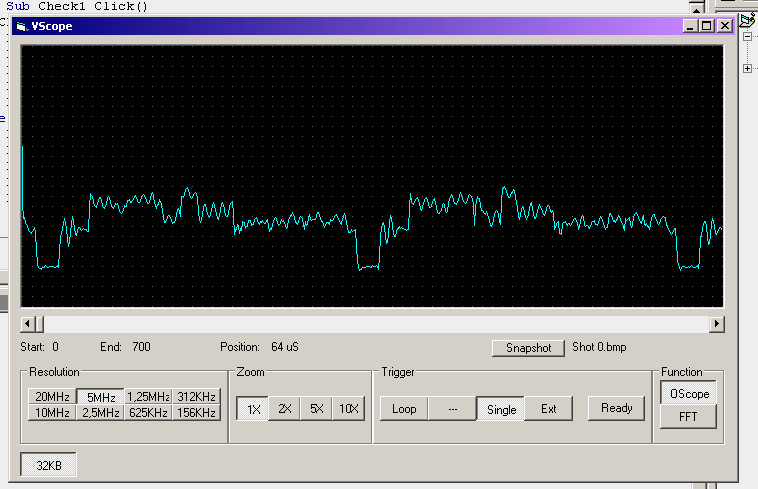

Програма цифрового осцилографа має більш просунутий інтерфейс. Тут показані кілька захоплених рядків відеосигналу PAL. Крім усього іншого я додав функцію аналізатора спектра. БПФ проводиться на 512 точок.

Реально можна спостерігати форму сигналів з частотою десь до 1 / 20-1 / 10 частоти дискретизації. Далі вже починає з'являтися алиасинг і форма сигналу досить сильно спотворюється. Спектр можна дивитися до 1/2 частоти дискретизації. Вище проявляється стробоскопічний ефект і спектр інвертується.

исходник осцилографа

Протокол спілкування приставки з комп'ютером будується наступним чином. Від ПК йдуть однобайтові команди, що керують роботою. В сторону ПК - пакети, розмір яких визначається обраним режимом. Після закінчення перетворення в ПК шле пакет даних. Коли ПК обробить його і буде готовий до прийому нового, то він посилає в приставку команду початку нового перетворення.

Примітка. В ході експериментів схема неодноразово змінювалася і допрацьовувалася. Хоча я і намагався задокументувати зміни, але я не можу стверджувати що схема 100% правильна. Ви можете використовувати її для розуміння принципу роботи системи. З цієї ж причини не рекомендується братися за неї початківцям радіоаматорам.

Ідеї щодо спрощення. Запхнути всю цифрову частину на дрібній логіці в якусь ПЛМ. Тоді все пристрій буде включати в себе не більше 8-10 корпусів. Я підібрав відповідні за ціною мікросхеми сімейства MAX3000 від ALTERA. Можливо, що скоро вдасться погратися і з ними.

Схожі проекти:

http://vereschagin.net/

На головну